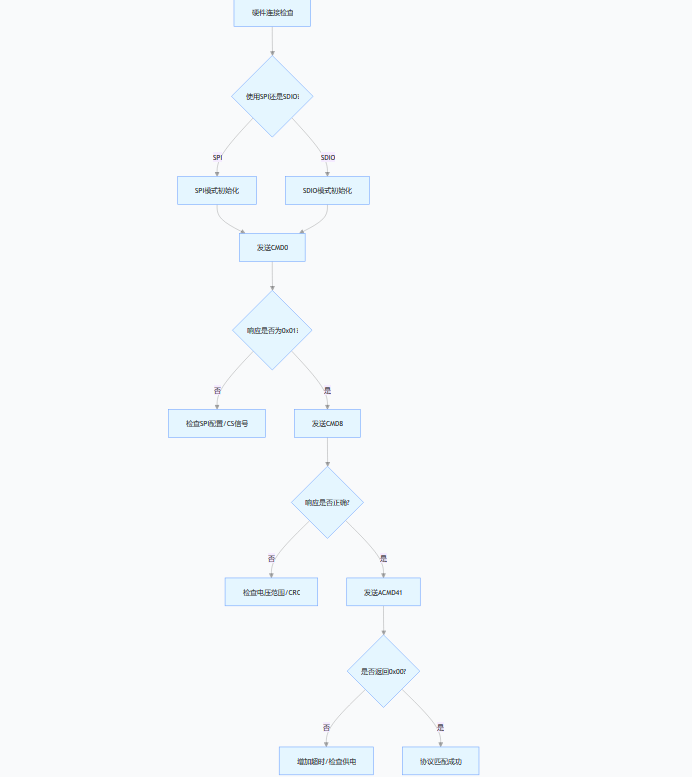

确定杰理主控与 SD NAND 之间的通信协议是否匹配,需要从硬件配置、软件驱动、通信波形三个层面进行系统性验证。以下是具体步骤和方法:

检查方法:

用万用表测量引脚连接,确认是否与主控和 SD NAND 的数据手册一致。

测试步骤:

// 杰理主控SPI初始化示例spi_config.mode = SPI_MODE_MASTER;spi_config.direction = SPI_DIRECTION_2LINES;spi_config.clock_polarity = SPI_POLARITY_LOW;spi_config.clock_phase = SPI_PHASE_1EDGE;

SDIO 模式:

需配置总线宽度(1 线 / 4 线)和时钟频率:

// 杰理主控SDIO初始化示例sdio_config.bus_width = SDIO_BUS_WIDTH_4BIT;sdio_config.clock_freq = 400000; // 初始化阶段≤400kHz

关键代码检查:

// 发送CMD0并接收响应uint8_t SendCommand(uint8_t cmd, uint32_t arg, uint8_t crc) {

uint8_t response;

uint8_t cmd_buffer[6] = {cmd | 0x40,

(arg >> 24) & 0xFF,

(arg >> 16) & 0xFF,

(arg >> 8) & 0xFF,

arg & 0xFF,

crc};

// 发送命令

SPI_Transfer(cmd_buffer, 6);

// 接收响应

do {

response = SPI_ReceiveByte();

} while (response == 0xFF);

return response;}SDIO 波形特征:

| 现象 | 可能的协议问题 |

|---|---|

| CMD0 无响应 | - SPI/SDIO 模式配置错误 - CS 信号时序异常 |

| CMD8 返回 0x05(参数错误) | - SDIO 模式下 CRC 校验失败 - 参数格式错误 |

| ACMD41 超时 | - 未正确切换到 SPI 模式(SD NAND 仍处于 SD 模式) |

| 数据传输错误 | - 块长度未设置(需 CMD16) - 时钟相位 / 极性不匹配 |

通过以上步骤,可系统性定位杰理主控与 SD NAND 之间的协议不匹配问题。若问题仍未解决,请提供具体的波形截图、代码片段和错误日志,以便进一步分析。

电话:176-6539-0767

Q Q:135-0379-986

邮箱:xcz@xczmemory.cn

地址:深圳市联创商务中心13层1308室