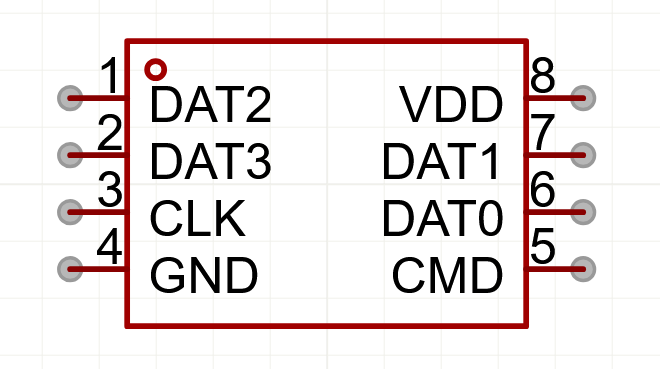

SDNAND是一种非易失型的内存技术,通常用于嵌入式系统中作为闪存来存储数据。在硬件设计中,SDNAND芯片需要通过特定的引脚与主控制器进行通信。以下是一个示例,展示了如何定义SDNAND相关的引脚定义。

SDD2、SDD3、SDD1和SDD0:这四个引脚用于传输数据。SDNAND芯片的数据传输可以使用4位或8位模式,具体使用哪种模式取决于协议。4位模式具有更好的兼容性,而8位模式传输速度更快,但需要更多的引脚。

SCLK:时钟线,用于传输时钟信号,SDNAND芯片和主控之间通过时钟信号同步数据传输。

CMD:命令线,用于传输命令。根据协议的不同,命令的长度可能是6位、17位或23位。

VSS:地线,提供SDNAND芯片的地。

VCC:电源线,提供SDNAND芯片的电源。

// 假设我们正在设计一个基于FPGA的嵌入式系统,并且我们使用的是Xilinx的FPGA。

// 对于SDNAND的控制信号,我们可能需要以下的管脚定义:

module sd_nand_controller(

input clk,

input rst_n,

// SDNAND 控制信号

output cs_n, // 片选信号

output we_n, // 写使能信号

output oe_n, // 读使能信号

output wp_n, // 写保护信号(可选)

output byte_n, // 字节选择信号(用于选择数据段)

// 数据通信信号

inout [7:0] data, // 双向数据线

// 命令、地址、设备选择信号

output [7:0] cmd, // 命令输出

output [27:0] addr, // 地址输出

output ce_n, // 设备选择信号

// 状态输出信号

input rdy_n, // 就绪/忙信号

input busy, // 忙信号

input rst_n, // 复位完成信号

input wp // 写保护信号(可选)

);

// 在这里实现SDNAND的控制逻辑

在这个例子中,我们定义了SDNAND所需的控制信号和数据通信信号。这些信号需要根据具体的SDNAND芯片的引脚定义来配置。在实际的硬件设计中,这些信号将通过物理层连接到SDNAND存储芯片。

上一篇:贴片SD卡能替代TF卡

电话:176-6539-0767

Q Q:135-0379-986

邮箱:xcz@xczmemory.cn

地址:深圳市联创商务中心13层1308室