根据 SDIO 时序图进行电路设计时,需要从信号完整性、时序匹配、电源管理和 EMI(电磁干扰)等多方面综合考虑。以下是具体的设计步骤和关键点:

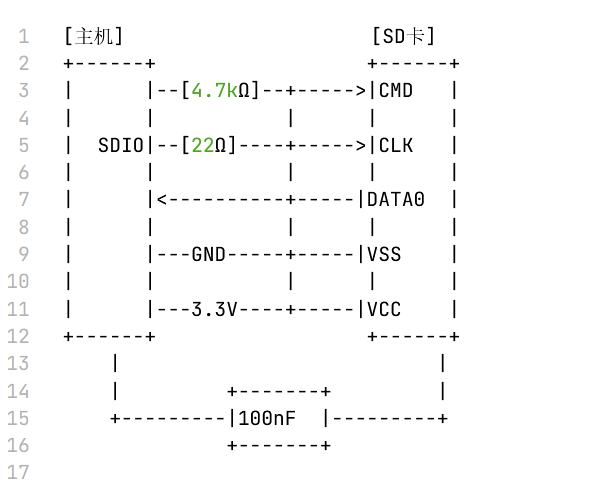

以下是一个简化的 SDIO 电路设计示例(1 位模式,3.3V 系统):

这个设计涵盖了基本的连接、上拉电阻和去耦电容。实际应用中,需根据具体设备和频率要求进行调整。

通过以上步骤,可确保 SDIO 电路在时序、信号质量和可靠性方面满足设计要求,实现稳定的数据传输。

上一篇:SDNAND的SDIO时序

下一篇:GD32F303RC的SD卡程序

电话:176-6539-0767

Q Q:135-0379-986

邮箱:xcz@xczmemory.cn

地址:深圳市联创商务中心13层1308室