关于SD NAND(特别是贴片式TF卡或SPI NAND Flash)是否需要阻抗匹配,答案是:取决于接口类型和工作频率。

我们来分两种情况讨论:

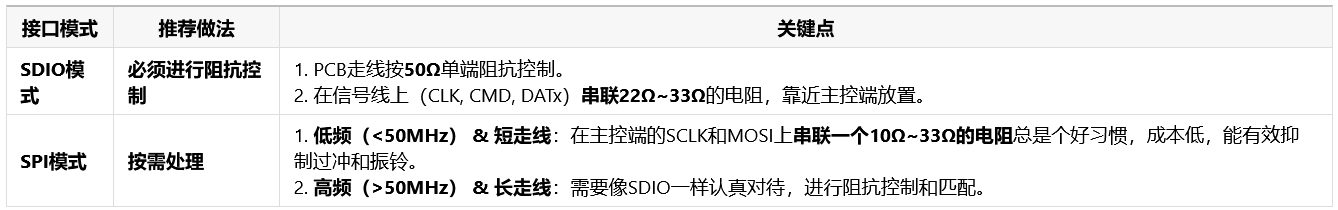

当你的SD NAND工作在SDIO模式(即使用CLK, CMD, DAT[0:3]信号线)时,答案是:通常需要,尤其是当走线较长或时钟频率很高时。

为什么需要?

SDIO总线(特别是SD/SDIO规范版本2.0及以上,支持高速模式)的工作频率可以达到50MHz、100MHz甚至更高。在如此高的频率下,信号边沿非常陡峭,PCB走线不再仅仅是简单的导线,而是呈现出传输线的特性。如果传输线的特征阻抗不匹配,就会导致信号反射,引起:

过冲和下冲

振铃现象

眼图闭合

时序错乱,导致读写错误或完全无法识别设备

怎么做?

目标阻抗: SDIO总线(包括CLK, CMD, DAT0-DAT3)的单端特征阻抗通常设计为 50Ω。

实现方法:

串联匹配电阻: 最常见的方式是在驱动端(通常是主控SOC的SDIO引脚附近)为CMD和DAT[0:3]每条信号线串联一个小阻值的电阻(例如22Ω或33Ω)。这个电阻与驱动器的输出阻抗加上PCB走线阻抗,共同匹配到50Ω。

时钟线处理: CLK线通常也需要串联一个匹配电阻(如22Ω)。由于其频率最高,对信号质量要求也最高,有时还会要求靠近驱动器端放置。

PCB控制: 需要通过控制走线宽度、与参考地平面的距离、介电常数等来确保PCB走线本身的特征阻抗为50Ω。这通常需要与PCB板厂沟通,使用阻抗计算工具(如SI9000)进行计算和控制。

结论: 对于SDIO模式,即使初始设计在低速下能工作,为了信号的稳定性和可靠性,强烈建议按照50Ω阻抗进行设计并添加串联匹配电阻。

当你的SD NAND工作在SPI模式(即使用CS, SCLK, MOSI, MISO信号线)时,答案是:通常不需要,或者在较低频率下可以简化处理。

为什么通常不需要?

频率较低: SPI接口的操作频率通常远低于SDIO模式。虽然SPI理论上可以跑到很高(如100MHz以上),但大多数MCU和SPI NAND Flash的实用频率在50MHz以下,很多应用甚至在20MHz以下。

信号数量少: 只有4根信号线,相互干扰比9根的SDIO总线小。

驱动能力较强: 很多MCU的GPIO/SPI引脚驱动能力相对较强,对传输线效应不敏感。

什么情况下SPI接口也需要考虑?

高频操作: 如果你的设计需要将SPI时钟推到50MHz甚至更高。

长走线: 如果SPI信号线在PCB上走了很长的距离(例如,超过几英寸/十几厘米)。

恶劣的电磁环境: 板上有其他大功率、高频器件,容易产生干扰。

SPI接口的匹配建议(如果要做):

串联匹配电阻: 和SDIO类似,可以在驱动端为SCLK、MOSI、CS串联一个小的电阻(例如10Ω - 33Ω)。

MISO线: 这是从设备输出到主设备的线,匹配电阻应放在从设备输出端附近,但实际操作中通常只在主控端统一处理,或者不加。

源端串联匹配是最常用、最简单有效的方法。 终端并联匹配在SPI接口中较少使用,因为它会增加功耗。

通用最佳实践:

查阅数据手册: 务必仔细阅读你的主控芯片和SD NAND芯片的数据手册和应用笔记。厂商通常会给出明确的布局和匹配建议。

预留匹配电阻位: 无论在哪种模式下,在PCB设计时,都强烈建议为所有相关信号线预留串联电阻的焊盘(使用0Ω电阻或空白位)。这为你后续的调试和信号质量优化留下了极大的灵活性,成本增加微乎其微,却能避免整个板子返厂的风险。

保证完整地平面: 一个完整、连续的参考地平面是保证信号质量和控制阻抗的基础。

等长要求(SDIO): 对于SDIO的高速模式,DAT[0:3]信号线之间最好做等长处理,以确保时序一致性。

下一篇:小容量EMMC替代方案

电话:176-6539-0767

Q Q:135-0379-986

邮箱:xcz@xczmemory.cn

地址:深圳市联创商务中心13层1308室