SD NAND 的原理图并不复杂,其核心是遵循 SD 物理层规范 (SD Physical Layer Specification)。

SD NAND 的本质是 将 NAND Flash 晶圆、控制器(Controller)和 被动元器件 封装在一个小尺寸的 LGA-8 或 TSOP-8 芯片内,对外提供一个标准的 SD 接口(兼容 SPI 模式)。因此,它的原理图连接与一个标准的 SD 卡座非常相似。

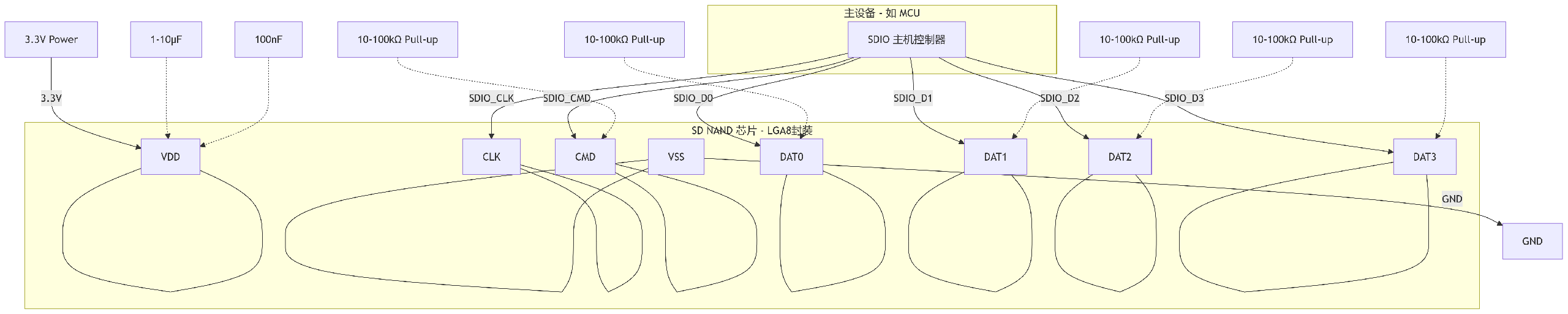

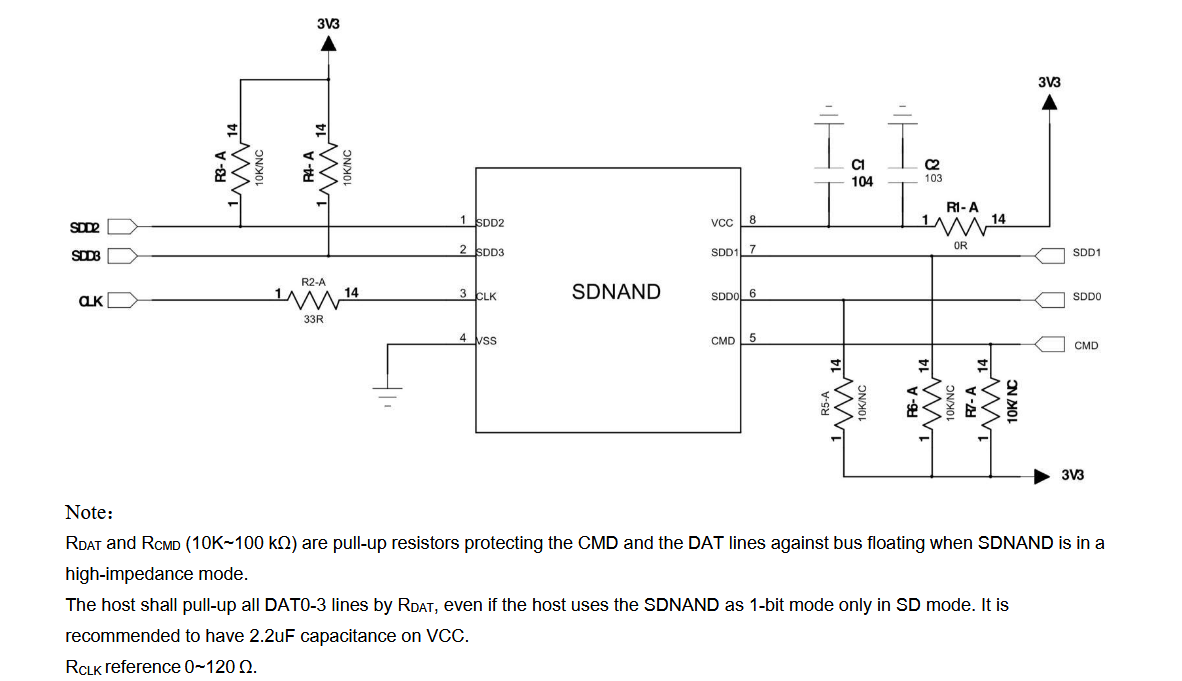

下图清晰地展示了一个典型的 SD NAND (以 LGA-8 封装为例) 在 SD 模式下的硬件连接原理:

上拉电阻 (Pull-up Resistors):

在 SD 模式下,DAT3 (CD/DO)、CMD (DI)、DAT0 (DO)、DAT1 (IRQ)、DAT2 (NC) 线上通常需要加上拉电阻(通常为 10kΩ - 100kΩ),尤其是在总线有多个设备时,用于确保在空闲状态时信号线处于高电平,提高稳定性。

在 SPI 模式下,CS、MOSI (DI) 线通常也需要上拉。具体请参考您主控芯片的数据手册建议。

电源去耦 (Power Decoupling):

VDD 和 VSS 引脚附近必须放置一个 0.1uF - 1uF 的陶瓷去耦电容,且尽可能靠近芯片引脚,以滤除电源噪声,确保芯片工作稳定。一个大一点的电容(如 10uF)进行电源缓冲也是很好的实践。

信号线布线 (Signal Routing):

CLK 是时钟信号线,容易产生电磁干扰,布线时应尽量短,并远离其他敏感信号线。

如果工作频率较高(>25MHz),所有数据线和命令线应尽量保持 等长 和 阻抗控制,以避免信号时序问题。

避免在 SDIO 信号线附近布置高频或开关信号,以防止噪声耦合。

卡检测 (Card Detection):

有些 SD NAND 芯片会借用 DAT3 引脚作为卡检测(CD)信号。如果需要此功能,需要根据芯片手册进行配置,通常需要一个下拉电阻。如果不需要,如上图所示,将其上拉即可。

在硬件连接正确的基础上,软件方面你需要:

初始化 SDIO 或 SPI 控制器:配置主控的 SDIO 主机控制器或 SPI 控制器,使其时钟、数据格式等符合 SD 协议。

发送命令序列:通过发送 CMD0 (GO_IDLE_STATE)、CMD8 (SEND_IF_COND)、ACMD41 (SD_SEND_OP_COND) 等命令序列来初始化 SD NAND 芯片,使其进入就绪状态。

读取 OCR 寄存器:通过 CMD58 读取操作条件寄存器,确认芯片的电压范围是否匹配。

读取 CSD/CID 寄存器:获取卡的特定信息,如容量、块大小、制造商ID等。

设置块长度:通常使用 CMD16 设置块大小为 512 字节(标准)。

进行读写操作:

单块读: CMD17 (READ_SINGLE_BLOCK)

多块读: CMD18 (READ_MULTIPLE_BLOCK)

单块写: CMD24 (WRITE_BLOCK)

多块写: CMD25 (WRITE_MULTIPLE_BLOCK)

停止传输: CMD12 (STOP_TRANSMISSION)

大多数嵌入式平台(如 STM32 的 HAL 库、ESP-IDF 等)都提供了完善的 SDIO 驱动库,你通常不需要从底层实现这些命令,只需调用相应的库函数进行初始化和管理即可。

总的来说,SD NAND 的原理图连接非常简单,几乎等同于一个“焊死在板子上的SD卡”。硬件设计的核心是 稳定的电源 和 干净的信号。软件上则依赖于主控平台的 SDIO 驱动库来完成底层通信。

最重要的参考资料始终是你所使用的特定型号的 SD NAND 数据手册 (Datasheet) 和 你主控芯片的参考手册 (Reference Manual)。

电话:176-6539-0767

Q Q:135-0379-986

邮箱:xcz@xczmemory.cn

地址:深圳市联创商务中心13层1308室