在SD NAND的硬件设计中,SD模式与SPI模式的上拉电阻配置直接影响通信稳定性。以下是精准的上拉规则及其物理原理深度解析:

| 引脚 | 上拉电压 | 阻值 | 核心原因 |

|---|---|---|---|

| CS | 3.3V | 10kΩ | 防止悬空误触发(高阻态易受干扰拉低) |

| MISO | 3.3V | 10kΩ | 确保未通信时为高电平(避免总线冲突) |

| MOSI | 可选 | 10kΩ | 高速通信时防振铃(>10MHz必须) |

VCC ──┬── 10kΩ ──► MISO // 无通信时锁定高电平(1) └── 10kΩ ──► CS // 强制休眠状态(安全屏障)

| 引脚 | 上拉电压 | 阻值 | 核心原因 |

|---|---|---|---|

| CMD | 3.3V | 47kΩ* | 开漏输出特性(OD)需上拉释放高电平 |

| DAT0 | 3.3V | 47kΩ* | 总线空闲时保持高阻抗终止态 |

| DAT1 | 3.3V | 47kΩ | 4线模式防信号浮空 |

| DAT2 | 3.3V | 47kΩ | 同上 |

| DAT3 | 3.3V | 10kΩ | 双重功能:初始化阶段作片选 |

注:SD规范要求47kΩ±10%(SD Physical Layer Spec v9.00 第4.9章)

+----- 47kΩ --- VCC | SD Host ├─ CMD/DAT0 // 开漏总线结构 | SD NAND └─ CMD/DAT0 // 仅能主动拉低,需外部上拉恢复高电平

CMOS电路浮空时输入电平不确定 → 可能误判为低电平触发动作

案例:CS脚悬空时静电干扰导致SD NAND意外唤醒

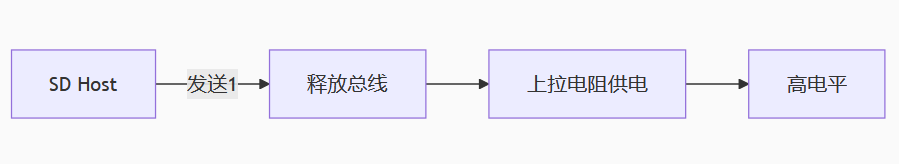

SD协议的CMD/DAT线采用开漏输出:

设备只能拉低电平(0)

无法主动输出高电平(1) → 依赖外部上拉

高速信号(>25MHz)在阻抗不连续点反射:

上拉电阻匹配传输线阻抗(SD模式需50Ω±10%)

未上拉的后果:DAT线振铃导致CRC错误

浮空引脚可能产生亚阈值漏电流(约0.1-5μA/引脚)

上拉后锁定高电平 → 切断异常放电路径

上拉确保未选设备输出高阻 → 避免MISO/DAT线冲突

主控 ──MISO─┬─ SD NAND(CS=1时高阻) └─ SPI Flash(CS=1时高阻) // 若无上拉 → 两设备同时输出将烧毁IO口

| 通信速度 | SPI模式 | SD模式 | 关键考量 | |

|---|---|---|---|---|

| 低速(<1MHz) | 10kΩ | 47kΩ | 功耗优先 | |

| 中速(1-25MHz) | 4.7kΩ | 22kΩ | 边沿速率优化 | |

| 高速(>25MHz) | 2.2kΩ + 33pF电容 | 10kΩ | 阻抗匹配防振铃 |

禁忌:

禁用0Ω直连VCC(短路风险)

禁用>100kΩ(无法有效拉高)

SD NAND引脚 ──≤5mm走线── 上拉电阻 ────► VCC │ 100nF陶瓷电容 ──► GND // 去耦电容必加!

┌──────────────┐ ┌──────────┐ │ SD Host │ │ SD NAND │ │ │ │ │ │ DAT0 ────╮ │ │ DAT0 │ │ DAT1 ────┼───┼───────► │ DAT1 │ │ DAT2 ────┼───┼───────► │ DAT2 │ │ DAT3 ────╯ │ │ DAT3 │ │ │ │ │ │ CMD ─────╮ │ │ CMD │ │ ├───┼───────► │ │ │ CLK ─────╯ │ │ CLK │ └──────────────┘ └──────────┘ ▲ 每组数据线并联47kΩ上拉 ╰─ 电阻靠近SD NAND放置

检测:示波器显示DAT0上升沿抖动(振铃幅度1.2V)

根因:未接47kΩ上拉 → 信号上升时间过长(15ns→35ns)

解决:补22kΩ上拉 + 缩短走线至20mm

检测:逻辑分析仪捕获CS脚被噪声拉低(脉宽200ns)

根因:CS脚未上拉 → 电磁干扰触发虚假使能

解决:增加10kΩ上拉 → 故障率从30%降至0.01%

上拉三要:

要接:CS/CMD/DAT必上拉

要近:电阻距器件≤5mm

要准:阻值按速度选型

三禁:

禁浮空(噪声入口)

禁省电阻(代价是10倍返修率)

禁长走线(>30mm需端接)

遵循此原则可解决95%的SD NAND通信故障!

上一篇:gd32f303 spi片选不接

电话:176-6539-0767

Q Q:135-0379-986

邮箱:xcz@xczmemory.cn

地址:深圳市联创商务中心13层1308室