以下是针对STM32F7驱动64GB SD NAND的完整指南,结合硬件设计、软件优化及数据记录仪应用场景,分为五个关键部分:

接口选择

SDIO四线模式:必须使用4-bit模式(D0-D3)以满足大容量存储带宽需求。一线模式仅适用于低速场景。

接线图:

STM32F7 → SD NAND SDIO_CK(PC12) → CLK SDIO_CMD(PD2) → CMD SDIO_D0(PC8) → D0 SDIO_D1(PC9) → D1 SDIO_D2(PC10) → D2 SDIO_D3(PC11) → D3 VCC(3.3V) → VCC GND → GND

电路设计

上拉电阻:所有数据线(D0-D3)和CMD需加10kΩ上拉电阻,确保信号稳定性。

去耦电容:VCC引脚并联0.1μF+10μF电容,抑制电源噪声。

走线优化:SD NAND走线长度≤50mm,避免与高频信号并行,减少EMI干扰

电源管理

独立3.3V LDO供电(如TPS73733),峰值电流需支持≥200mA,防止写入时电压跌落

SDIO初始化(STM32CubeMX配置)

时钟分频:初始化阶段≤400 kHz,工作阶段升至25-50 MHz(依SD NAND支持)。

总线宽度显式设置:

HAL_SD_ConfigWideBusOperation(&hsd, SDIO_BUS_WIDE_4B); // 启用4-bit模式

大容量存储支持

分区表:64GB需使用GPT分区表(MBR仅支持≤2TB,但嵌入式兼容性差)。

文件系统:

exFAT替代FAT32:支持单文件>4GB,集群大小建议64KB(平衡空间利用率与速度)。

FatFs配置:

#define _USE_EXFAT 1 // 在ffconf.h中启用exFAT#define _MAX_SS 4096 // 扇区大小匹配SD NAND(通常512B或4KB)

写入加速技术

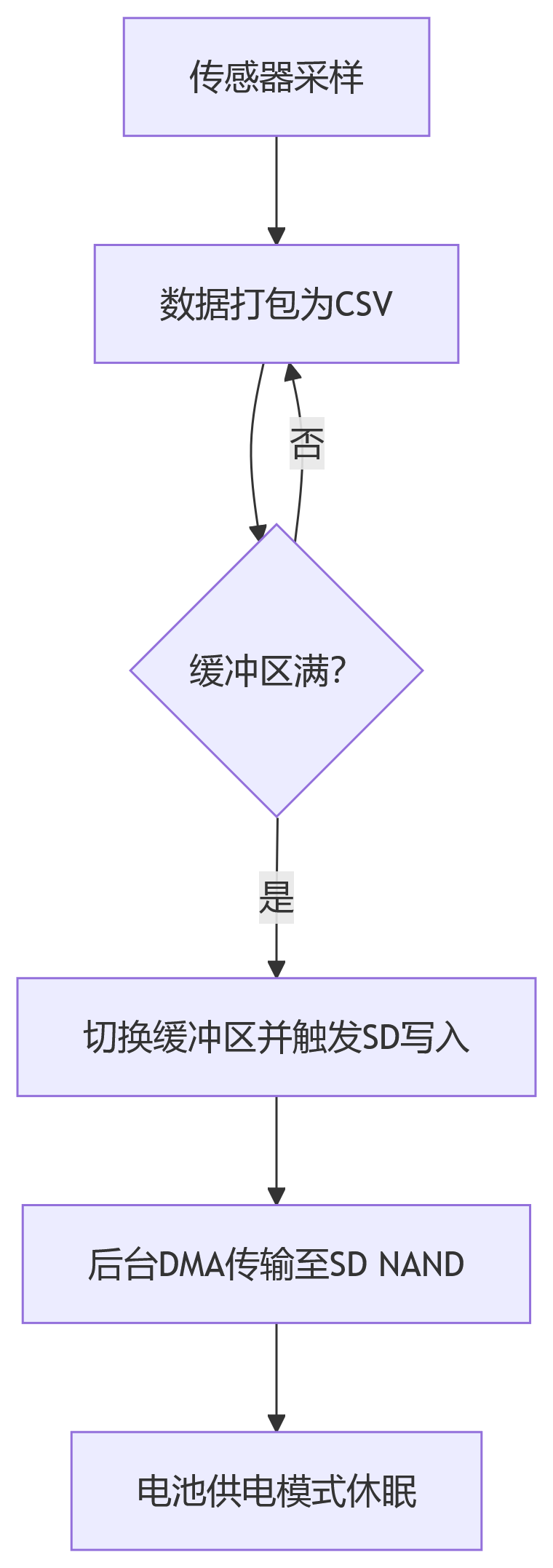

双缓冲机制:分配两个32KB RAM缓冲区(DTCM内存优先),交替进行DMA传输与数据填充

uint8_t buffer0[32768] __attribute__((section(".dtcm")));uint8_t buffer1[32768] __attribute__((section(".dtcm")));批量写入:每次写入≥16个扇区(8KB),减少f_sync()调用频率。测试表明,32KB缓冲区写入1MB数据仅需3秒。

中断与DMA配置

使用SDIO中断+IDMA(STM32F7专属)替代轮询,释放CPU负载。

设置DMA传输完成中断,避免f_write()阻塞

坏块与错误处理

使能硬件CRC:HAL_SD_Init()中启用SDIO硬件流控。

定期调用f_check_fs()检测文件系统一致性,预防断电丢数据

数据流架构

关键参数设计

采样率支持:300字节/样本@100Hz时,需吞吐量30KB/s(四线SDIO轻松满足)2。

续航优化:

写入间隙切至Stop模式(电流≈100μA)。

禁用SDIO时钟节省(__HAL_SD_SDIO_CLK_DISABLE())

PC兼容性

实现USB-MSC桥接:通过STM32内置USB OTG,将SD NAND模拟为U盘(无需拔卡)

写入延迟波动

症状:f_sync()耗时>10ms。

方案:增大写入缓冲区至≥64KB,减少sync调用次数。

容量识别失败

检查SD NAND是否支持SDHC/SDXC规范(64GB需SDXC)。

在HAL_SD_Init()后调用HAL_SD_ConfigWideBusOperation()前,执行HAL_SD_SetBusWidth()

文件系统崩溃

启用FATFS的异常保护:

#define _FS_REENTRANT 1 // 多线程保护#define _FS_LOCK 2 // 文件锁

性能对比表:不同配置下的写入速度参考47

| 模式 | 缓冲区大小 | 平均速度 | 适用场景 |

|---|---|---|---|

| 单线+轮询 | 512B | 50KB/s | 低速传感器 |

| 四线+DMA | 32KB | 330KB/s | 100Hz数据记录仪 |

| 四线+IDMA | 64KB | 600KB/s | 音频/视频流记录 |

通过上述方案,STM32F7可稳定驱动64GB SD NAND,满足工业级数据记录仪的长时、高可靠存储需求。完整工程示例参考,硬件设计规范详见。

上一篇:SDFLASH内部有坏块管理吗?

电话:176-6539-0767

Q Q:135-0379-986

邮箱:xcz@xczmemory.cn

地址:深圳市联创商务中心13层1308室